|

|

Главная » Микропроцессорное управление 1 ... 5 6 7 8 9 10 11 ... 27 3. Медленный дрейф напряжений С/ и Uq не влияет на результат преобразования, так как в данном случае важна лишь кратковременная стабильность этих напряжений в течение интервала времени Tq. 4. В интегрирующих ПНК уменьшается влияние всех видов помех. Помехи с частотой питающей сети будут полностью подавляться, если выбрать время интегрирования Tq входного напряжения равным периоду питающей сети Т^. Чтобы обеспечить это условие, осуществляется подстройка частоты генератора импульсов G под частоту питающей сети. 5. Время полного цикла преобразования достаточно велико и составляет несколько десятков миллисекунд. Преобразователи напряжения в код с компенсационным интегрированием используются, как правило, для преобразования постоянных или медленно изменяющихся напряжений, получаемых от высокочувствительных датчиков температуры или расхода. Относительная погрешность преобразования этих ПНК не превосходит 0,1%. Пример построения УСО на базе АЦП с компенсационным интегрированием. На рис. 2.16 представ-пена структурная схема 12-разрядного АЦП с компенсационным интегрированием типа напряжение - временной интервал - код , предназначенного для преобразования в код напряжений произвольной полярности и величины. Аналого-цифровой преобразователь включает в свой состав: интегратор DAI; компаратор DA2; формирователь импульсов Ф, формирующий положительные импульсы по переходам выходного сигнала компаратора из состояния О в состояние Ь> или из состояния 1 в состояние О ; схему управления, состоящую  Рис. 2.16. Структурная схема 12-разрядного АЦП с компенсационным интегрированием типа напряжение-временной интервал-код

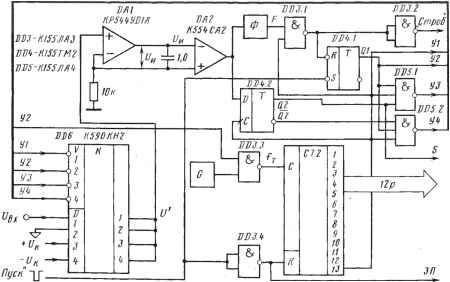

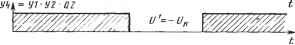

uii= 41- уг-пг  Рис. 2.17. Временные диаграммы сигналов АЦП из Л5-триггера DD4.1, тактируемого jD-триггсра DD4.2, логических элементов ООЪ и DD5\ коммутатор аналоговых напряжений jDD6; генератор импульсов (ГИ) и 13-разрядный двоичный счетчик СТ2. На входы АЦП подаются следующие сигналы: измеряемое постоянное напряжение С/< = 0...10В произвольной полярности; О В (земля); компенсирующие напряжения + С/ и - t/ ; управляющий сигнал Пуск (импульс отрицательной полярности). С выходов АЦП поступают следующие сигналы: Строб , используемый для записи выходного кода в регистр ввода; признак знака S\ 12-разрядный выходной код; сигнал записи ЗП кода номера канала в буферный регистр. В схеме управления формируются также сигналы У1. Y2, УЗ, К4, используемые для коммутации аналоговых напряжений U, ОВ, +U, -С/, соответственно. Кроме того, сигнал Y2 управляет состоянием ключа DD3.3. Рассмотрим работу этого АЦП (рис. 2.17). С приходом внешнего управляющего сигнала Пуск (в момент времени fo) /?5-триггер DDAA устанавливается в состояние 1 и открывается ключ DD3.3, через который на тактовый вход счетчика СТ2 поступают импульсыЭтот же сигнал Пуск через инвертор DDiA подается на вход R счетчика и устанавливает его в состояние О , после чего счетчик работает в режиме суммирования. Уровнем логического О , снимаемым с самого старшего разряда счетчика (сигнал открывается ключ 1 коммутатора DD6 и на вход интегратора DA\ поступает напряжение произвольной полярности. Сигнал с выхода интегратора поступает на вход компаратора DA2. сигнал на выходе которого имеет уровень логического О , если полярность напряжения t/ -положительная, и уровень логической 1 , если полярность U -отрицательная. Заметим, что в режиме интегрирования напряжения полярность его совпадает с полярностью напряжения t/ . При изменении сигнала Y\ происходит запись значения признака знака S в триггер DDA.l и в зависимости от этого значения один из сигналов КЗ или К4 принимает уровень логического О . Если б момент времени /j полярность напряжений и С/ положительная (5=22 = 0). то К4 = 0, и на вход интегратора поступает напряжение U= - U отрицательной полярности; если же полярность напряжений и отрицательная, то КЗ=О, и на вход интегратора поступает напряжение U= + U положительной полярности. В момент времени ь. когда полярность напряжения U на выходе интегратора из.меняется, на выходе формирователя ФИ появляется импульс F положительной полярности. При этом Д5-триггер £)jD4.1 устанавливается в состояние О , ключ DD3.3 закрывается и счетчик СТ2 переходит в режим хранения информации. В этот же момент времени на вход интегратора подается напряжение [/=0В. На этом цикл преобразования заканчивается. На выходе АЦП фиксируется 12-разрядный код, пропорциональный значению 1, и признак знака S. На рис. 2.18 представлена схема подключения УСО к системной магистрали И-41, Устройство связи с объектом включает коммутатор каналов К (мультиплек- KP59DKH1

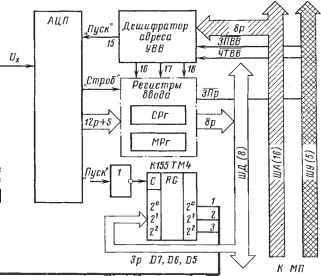

о +5В  Рис. 2.18. Схема подключения УСО к магистрали И-41 76 Ц ЛЦП (I..l2p -информационные, 13р - S 1знан1Чр-Строб, 15р-,Пуск ) -Wi- Н155ИЛЭ

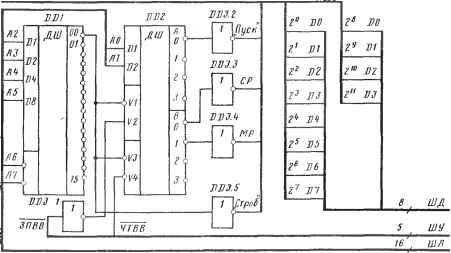

DHZ HlSSnUk К155ЯИ1 VBS) Ьуз г9№ пвз К5В9ИГП Ъвмз ьмг с /г МРг *5В

Рис. 2.19. Схема подключения дешифраторов и регистров ввода УСО к системной магистрали И-41 сор), 12-разрядный АЦП (см. рис. 2.16) и интерфейс на базе дешифратора адреса УВВ, двух регистров ввода СРг (регистра старшего байта) и МРг (регистра вывода номера канала RG). Схема подключения дешифраторов адресов УВВ и регистров ввода СРг и МРг к системной магистрали И-41 показана- на рис. 2.19. Для адресации внешних устройств используются восемь младших разрядов (Л7-Л0) шины адреса ША. Шесть из них (7-2) подсоединяются к входам дешифратора £)£)1, который позволяет подключить и осуществить выбор до 16 УСО. Дешифратор DD2 стробируется выходным сигналом с дешифратора DD\ и служит для дешифрации двух младших адресных разрядов А\ и ЛО с целью формирования сигналов Пуск (15), Установка в О (18). ВМ (16, 17). Значения входных и выходных сигналов DD2 представлены в табл. 2.3 (при условии, что с выхода DD\ поступает уровень логического О ). В данном примере предполагается, что кол адреса УСО равен А1 АЬ АЪ А4 A3 А2 А\ /10 = 000000А'А', где произвольное значение ( 1 или О ) сигнала. Преобразователь напряжения в код поразрядного уравновешивания. Рассмотрим принцип действия широко распространенного преобразователя поразрядного уравновешивания (рис. 2.20, а). Входное напряжение поступает на один из входов схемы сравнения СС, на второй вход которой с выхода преобразователя кода в напряжение (ПКН) подается сумма эталонных напряжений пкн, соответствуютцая определенному двоичному коду. Дискретный сигнал с выхода схемы сравнения поступает на вход регистра последовательного приближения (РПП), на другие входы которого подаются тактовые импульсы (ТИ) с генератора импульсов G и сигнал Пуск , соответствующий началу цикла преобразования. Таблица 2.3. Таблица функционирования дешифратора DD2 Информационные т (А\) D\ (AQ) Управляющие входы Группа А 0 12 3 Примечание 0 111 Сигнал Пуск . Запись кода в RG 10 11 Установка в состояние О СРг и МРг 110 1 1110 D2 {А\) D\ (/10) Группа В 0 12 3 ВМ ВМ 0 111 Чтение СРг 10 11 Чтение МРг 110 1 1110 Выходы РПП являются выходами ПКН. Число информационных выходов ПКН соответствует числу разрядов двоичного кода. Кроме этого, РПП формирует сигнал конца преобразования КПр, соответствующий концу цикла преобразования. На рис. 2.20, б представлены временные диаграммы сигналов четырехразрядного ПКН последовательного приближения (поразрядного уравновешивания). Преобразование напряжения в код начинается с приходом сигнала Пуск . При этом на выходе старшего разряда РПП устанавливается 1 , на остальных выходах - О , т.е. % = а2 = а1 = а^0 и двоичный код 30210 = 1000. С приходом каждого тактового импульса ТИ устанавливается 1 в следующем по старшинству разряде (аг=1), пни ----1 /<Пр РПП ТИ 1 Пуси и л ПВО Uf>UnKH 1011 Рис. 2.20. Преобразователь напряжение-код поразрядного уравновешивания: о обобщенная структурная схема, О временные диаграммы сигналов а значение ближайшего более старшего разряда а; +1 кода зависит от результата сравнения напряжений и [/пкн и выбирается равным: fl, если UUnKH, tf. --[0, если ,<пкн. - В конце преобразования ровно через п тактов, где п - число разрядов двоичного кода, регистр последовательного приближения свою работу заканчивает. На выходе РПП появляется сигнал КПр = 1, а напряжение уравновешивается напряжением Упкн- t/.[/пкн = Е 2%и, = и, Х 24, (2.7) 1=0 1=0 где Uq-напряжение, соответствующее младшему разряду кода; а,- значение О или 1 /-го разряда двоичного кода; 2 - вес /-го разряда двоичного кода. . Пуск CmpoS В PO- OP о- 1л г АЦП г- б ТИ К Руск Стро ВР П В к N1 Von цлп ОдР МдР ВшД В Пр Vfll  Вход тп в я г  Рис. 2.21. Цифроаналоговый и аналого-цифровой преобразователи поразрядного уравновешивания на основе БИС К572ПВ1: ги генератор импульсов: Т тумблер (ключ); DAI онераниониый уси;1итель гила 154УДЗ. К.>74УД1. К544УД2; DA2 комнараЕор нанряженип niria 521 САЗ На выходах ПКН фиксируется двоичный код, пропорциональный входному напряжению 1]. При подаче нового сигнала Пуск цикл преобразования повторяется. Время цикла преобразования определяется по формуле (2.8) период следования тактовых где п - число разрядов ПКН; т„ импульсов. Аналого-цифровой преобразователь поразрядного уравновешивания на основе БИС К572ПВ1. На рис. 2.21 представлена структурная схема маломощного 12-разрядного ЦАП и АЦП поразрядного уравновешивания, которая включает в свой состав: АЦП поразрядного уравновешивания (совместно с внешним усилителем и компаратором) с выводом параллельного двоичного кода; умножающий ЦАП совместно с внешним усилителем; байтовый параллельный интерфейс для согласования с 8-разрядной шиной данных. Назначение выводов БИС К572ПВ1 приведено в табл. 2.4. Функции, выполняемые микросхемой К572ПВ1. сведены в табл. 2.5. Схема подключения дешифраторов и АЦП К572ПВ1 (в составе УСО) к системной магистрали И-41 представлена на рис. 2.22. Таблица 2.4. Назначение выводов БИС К572ПВ1

К лцп /1з7гпв1 вт-шззивч гпЗ'Нтлн!  Рис. 2.22. Схе.ма подключения дешифраторов и АЦП К572ПВ1 к системной магистрали И-41 Окончание табл. 2.4

Таблица 2.5. Функции, выполняемые интегральной микросхемой К572ПВ1 Управляющие входы

Примечание: В режиме ЦАП выходы всех разрядов отключены. Устройство связи с объектом блока управления БУ-3 Орион-3 . Микропроцессорным устройством, позволяющим реализовать большой объем функций управления и строить весьма сложные системы управления за счет развитого УОС является блок управления БУ-3 Орион-3 , который широко применяется в системах управления оборудованием. В основе построения Орион-3 использован магистрально-модульный принцип. Структурная схема блока управления БУ-3 представлена на рис. 2.23. К магистрали МПИ подключаются модули Орион-3 : центральный процессор М2 микроэвм Электроника-бОМ (7); устройство оперативное запоминающее (2) и устройство постоянное запоминающее (3) объемом 4 К и 16 К 16-разрядных слов соответственно; контроллер связи со считывателем с перфоленты В1 (4); плата и панель управления (5, 6); модуль связи МС-5 (7), обеспечивающий связь с другими устройствами по каналам

|

Как выбрать диван  История мебели  Стили кухонной мебели  Публикации  Инверторы  Приемники |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||